## **ELEC50001 EE2 Circuits and Systems**

## **Problem Sheet 5 Solutions – Data Converters** (Lectures 10 and 13)

(Question ratings: A=Easy, ..., E=Hard. All students should do questions rated A, B or C as a minimum)

1B. Full-scale range = 3998 so the accuracy is 2/3998 of full-scale range. For an N-bit binary A/D converter, the full-scale range is  $(2^{N}-1)$  LSB giving an accuracy of  $0.5/(2^{N}-1)$ .

Hence

$$\frac{0.5}{2^N - 1} \le \frac{2}{3998} \implies 2^N \ge 1000.5 \implies N \ge 9.96 \implies N = 10$$

- 2B.  $-2047 \text{ mV} \pm 0.5 \text{ mV}$ , i.e. -2047.5 mV to -2046.5 mV.

- 3B. 1 V and 8 V correspond to output values of 100 and 800 respectively, so if 1 V < x < 8 V, the output will be in the range 100 to 799.

- 4C. A change of 5 V in V3 must give a change of -1 V in VOUT, a gain of -0.2. Hence RF/R3 =  $0.2 \Rightarrow$  R3 = 50 k $\Omega$ .

When V3=0, the op-amp may be viewed an a non-inverting amplifier with a gain of (1 + RF/R3) = 1.2. The voltage at VOUT due to V2:0 is therefore given by:

$$V_{OUT} = 1.2 \times \frac{G_2 V_2 + G_1 V_1 + G_0 V_0}{G_4 + G_2 + G_1 + G_0}$$

where G4:0 are the reciprocals of R4:0.

To minimize the effect of op-amp bias currents, we should make the Thévenin impedances at the input terminals equal. This means that  $G4+G2+G1+G0 = G3+GF = 120 \ \mu S$ .

The gains from V2, V1 and V0 to VOUT must be 0.1, 0.05 and 0.025 respectively. Thus we have  $G2 = 120 \ \mu\text{S} \times 0.1/1.2 = 10 \ \mu\text{S} \Rightarrow R2 = 100 \ \text{k}\Omega$ . Similarly, R1 = 200 k $\Omega$  and R0 = 400 k $\Omega$ .

Finally  $G4 = 120 \ \mu\text{S} - G2 - G1 - G0 = 102.5 \ \mu\text{S} \Longrightarrow \text{R4} = 9.8 \ \text{k}\Omega$ .

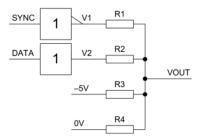

5C. The SYNC signal needs inverting because SYNC going high must cause the output to decrease. We will need a negative bias voltage in order to obtain -0.3 V. Our circuit is therefore:

Taking Gn = 1/Rn we must have  $G1+G2+G3+G4 = 1/50\Omega = 20$  mS.

Then VOUT =  $(V_1G_1 + V_2G_2 - 5G_3) / 20 \text{ mS}.$

From the truth table, we see that changes of 5 V in V1 and V2 must give changes in VOUT of 0.3 and 0.7 volts respectively; this means we need gains of 0.06 and 0.14. Hence:

$\begin{array}{l} G1 = 0.06 \times 20 \text{ mS} = 1.2 \text{ mS} \Rightarrow R1 = 833\Omega. \\ G2 = 0.14 \times 20 \text{ mS} = 2.8 \text{ mS} \Rightarrow R2 = 357\Omega. \\ \text{To generate the } -0.3 \text{ V offset: } 5G3 = 0.3 \times 20 \text{ mS} = 6 \text{ mS} \Rightarrow R3 = 833\Omega. \\ G4 = 20 \text{ mS} - G1 - G2 - G3 = 14.8 \text{ mS} \Rightarrow R4 = 67.6\Omega. \end{array}$

Note it is possible to take R4 to +5 V instead in which case R3 and R4 are  $116\Omega$  and  $135\Omega$ .

This circuit is very fast since it has no op-amps.

- 6B. The range of a 16-bit signed number is ±32767 and so to avoid distortion, the RMS value must be no higher than 3276.7. From the notes, the RMS value of quantisation noise is 0.289 LSB which gives a signal-to-noise ratio of 11338 which equals 81 dB

- 7C. Full-scale range of 20 V equals 4096 LSB so  $0.5 \text{ LSB} = 0.5 \times 20/4096 = 2.44 \text{ mV}$ .

The peak rate of change of a 10 V sinewave is  $20\pi f$  volts per second. The voltage change in 5 ns is therefore  $\pi f \times 10^{-7}$ . These are equal when  $f = 2.44 \times 10^{-3} \times 10^{7} / \pi = 7.77$  kHz.

For the second part I = C dV/dt from which  $\Delta t = C \times \Delta V/I = 2 \times 10^{-10} \times 2.44 \times 10^{-3}/10^{-9} = 488 \ \mu s.$